Home

SEMINATEC (Workshop on Semiconductors and Micro & Nano Technology) is focused on technology trends in the areas of micro and nanotechnology. In 2024 the SEMINATEC will be organized by Laboratory of Integrable Systems at the University of São Paulo (USP) and São Paulo State University (UNESP - campus of São João da Boa Vista), Brazil with support/funding from the EDS/IEEE South Brazil chapter, EDS Student Chapter of UNICAMP, EDS Student Chapter of FEI, SSCS/IEEE South Brazil chapter, the Brazilian Microelectronic Society. The goal of this event is to promote the interaction among industry, academy, research & development centers, government and students, all looking for real opportunities towards improving education, research, and technology.

The event will be held at the Paulo Ribeiro de Arruda Auditorium at Polytechnic School of the University of São Paulo (USP). The abstract is limited up to two pages (two columns) and be written in English and be sent electronically until March 17th. We invite the community to participate in the Tutorial and Poster Sessions that will happen during XVIII SEMINATEC, April 18th and 19 th , 2024.

The XVIII SEMINATEC welcomes the submission of original papers in all areas related to semiconductors, optoelectronic devices, optics, fabrication of micro & nano-structures, microsystems, device modeling, CAD, simulation and devices integrated circuits.

Fig. 1 - Test chip fabricated annually at USP during “Oficina de Fabricação de Circuitos Integrados MOS (tecnologia SOI nMOSFET)”

Fig. 1 - Test chip fabricated annually at USP during “Oficina de Fabricação de Circuitos Integrados MOS (tecnologia SOI nMOSFET)”

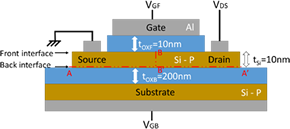

Fig.2 – Back Enhanced (BE) SOI MOSFET (Patent USP: BR102015020974-6, 2015).

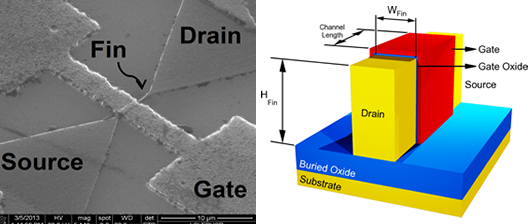

Fig. 3 – (a) First SOI FinFET (3D transistor) fabricated in Latin America with electron beam at USP in 2012 [1-3] and (b) Perspective view of triple gate SOI FinFET.

[1] Martino, J. A., Design, fabrication and electrical characterization of SOI FinFET transistors. Frontiers of Science, Salamanca, Spain, 2012, http://www.fapesp.br/fronteras/sal/martino.pdf.

[2] RANGEL, R., POJAR, M., SEABRA, A. C., SANTOS FILHO, S. G. and MARTINO, J. A., 3D Transistor (FinFET) Fabricated with Three Lithography. SEMINATEC 2013 - VIII Workshop on Semiconductors and Micro & Nano Technology. Campinas, proceedings SEMINATEC, 2013.

[3] RANGEL, R. C., Pojar, M., Seabra, A. C., Filho, S. G. S. and Martino, J. A., Fully electron-beam-lithography SOl FinFET. Symposium on Microelectronics Technology and Devices, SBMicro 2013, Curitiba, Proc. IEEExplorer, p.1-5, 2013.

Dates

Event:

April 18th and 19th, 2024

Deadline for abstract:

March 10, 2024

March 17, 2024

Acceptance Notification:

April 1, 2024